CIRCUIT:

CODE:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY BASIC_GATE IS

PORT(A,B:IN STD_LOGIC;

NAND_OUT,NOR_OUT,XOR_OUT,XNOR_OUT: OUT STD_LOGIC);

END BASIC_GATE;

ARCHITECTURE BEHAVIORAL OF BASIC_GATE IS

BEGIN

NAND_OUT <= NOT (A AND B);

NOR_OUT <= NOT (A OR B);

XOR_OUT <= (A AND NOT(B)) OR (NOT(A) AND B);

XNOR_OUT <= (A AND B) OR (NOT(A) AND NOT(B));

END BEHAVIORAL;

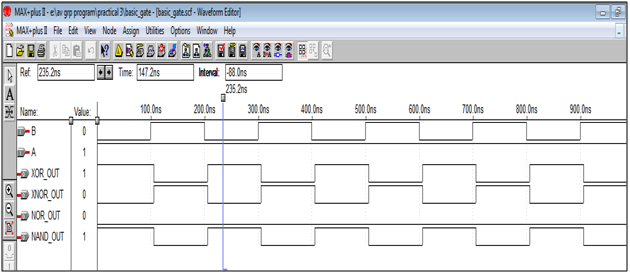

WAVE FORMS:

/*54745756836*/